PRESENTED BY

Dr. Rajesh Khatri (Associate Professor)

- What is VLSI?

- Very Large-Scale Integration

- Integration of gates or transistors?

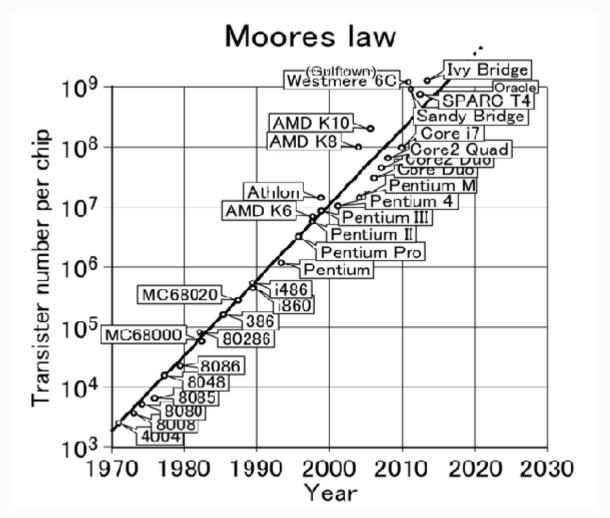

- SSI Small Scale Integration (0-10<sup>2</sup>)

- MSI Medium Scale Integration (10<sup>2</sup>-10<sup>3</sup>)

- LSI Large Scale Integration (10<sup>3</sup>-10<sup>5</sup>)

- VLSI Very Large-Scale Integration (>=10<sup>7</sup>)

➤ Moore's Law

- ➤ How to integrate millions and billions transistor?

- > Solution-

EDA Tools / CAD Tools

Electronic Design Automation Tools

- > Cadence

- > Synopsys

- ➤ Mentor Graphics (Siemens)

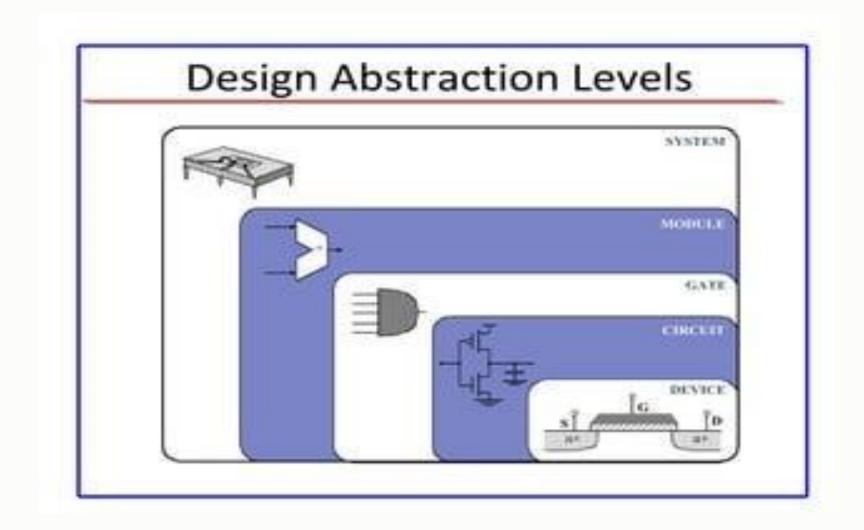

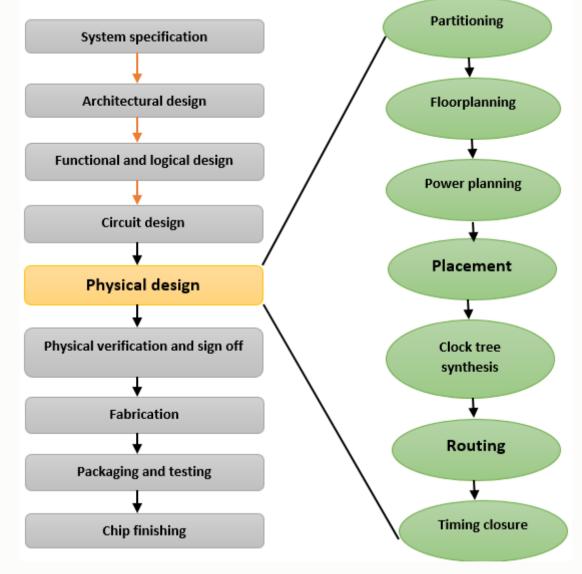

> Front end and Back end

Front end: initial conceptualization, system level description, architecture level, RTL coding

➤ Back end: Physical implementation, floor planning placement and routing

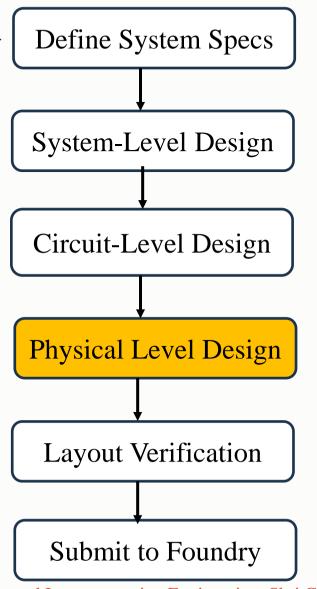

• Chip Design Flow

Schematic editor & Ckt Simulator - Spice

Layout editor, Design rule check (DRC)

Layout Vs Schematic (LVS), Spice for post layout simulation

Device Models (Model file)

Technology file, extraction file

Technology file, Device Models

#### Chip Design Flow

Model File:

• Technology File: The technology file provides information on various aspects, including layer definitions, design rules, spacing requirements, wire widths, and other parameters that guide the layout of the integrated circuit.

• PDK (Process Design Kit): It's a set of libraries and associated data (model files, physical verification rule files, control files for various tools) to allow you to design in a particular technology.

• PDK's: Vendors – gpdk- Generic PDK

SCL (Semi-conductor Laboratory)

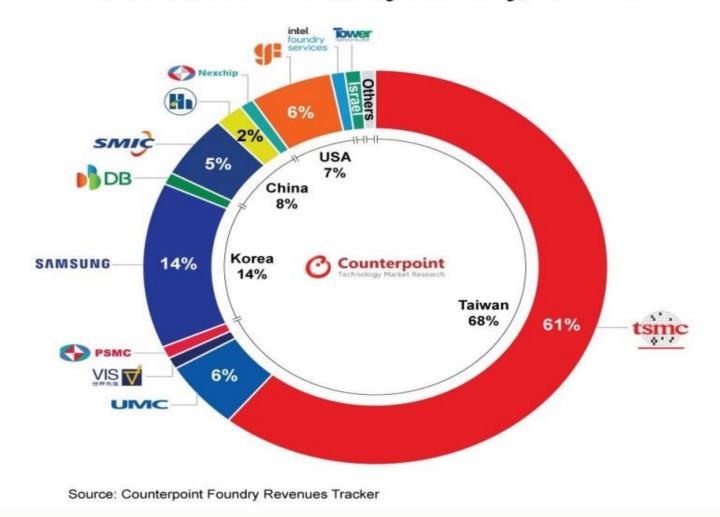

UMC – (United Microelectronics Corporation)

TSMC – (Taiwan Semiconductor Manufacturing Company)

**Tower Semiconductor**

Global Foundries

SMIC – (Semiconductor Manufacturing International Corporation)

#### Revenue Share of Key Players in Global Semiconductor Foundry Industry, Q4 2023

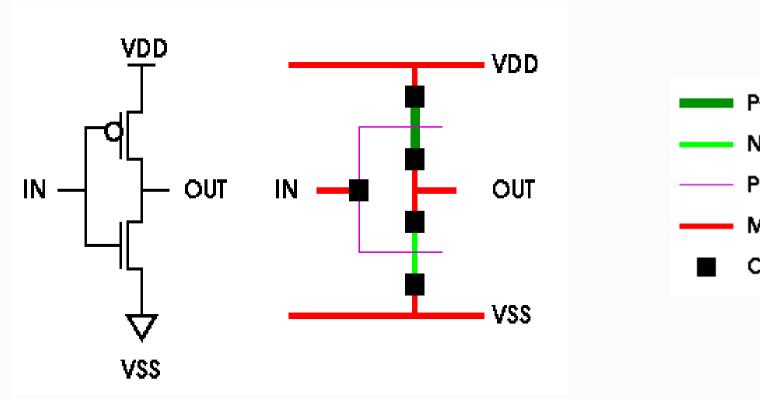

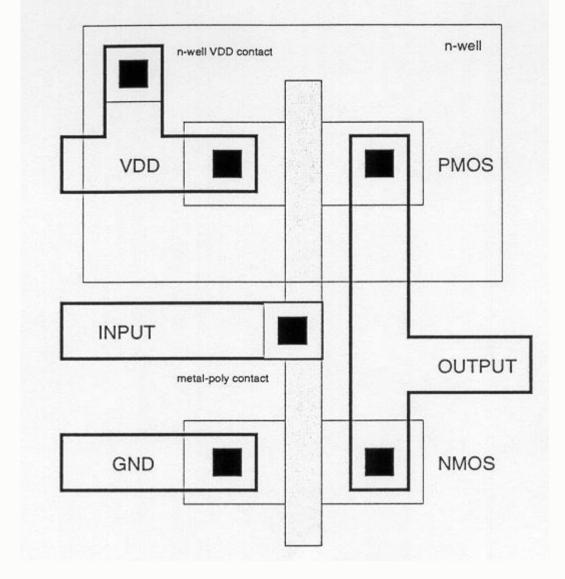

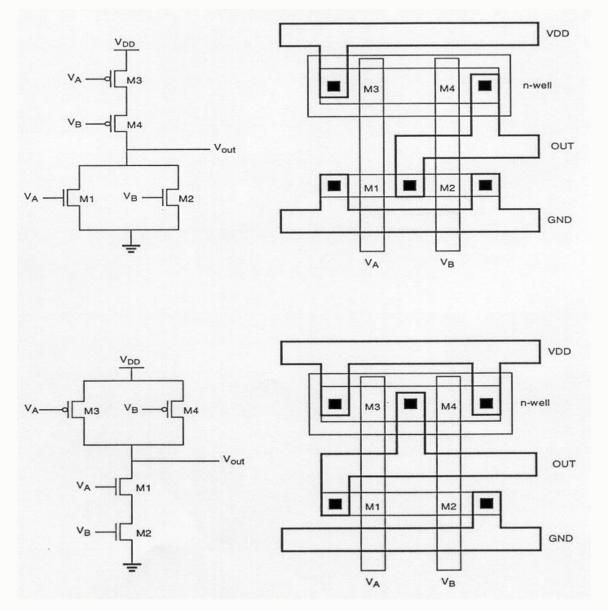

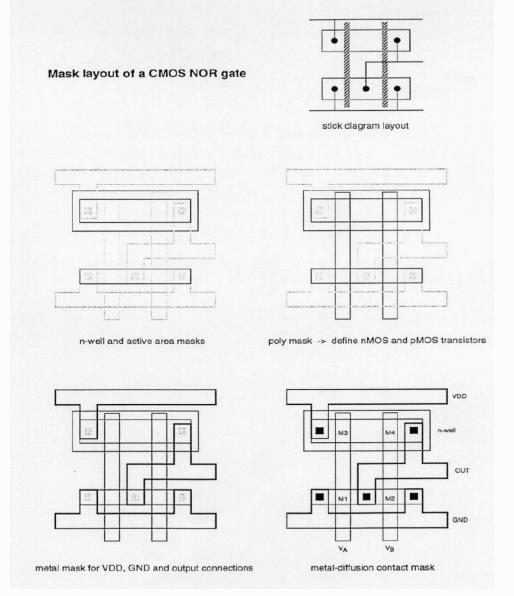

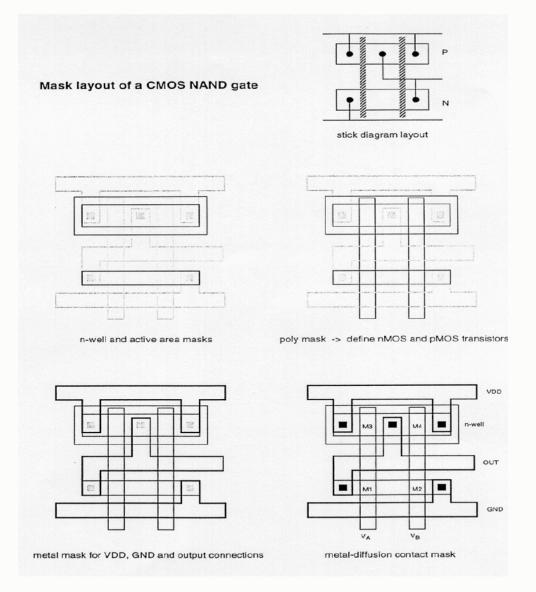

#### **✓ CMOS Inverter and Stick Diagram**

- Layout Design Rules

- Lambed Based Design Rules

- Micron based Design Rules

- Lambed Based Design Rules

- Expressed in terms of a scaling parameter: Lambda ( $\lambda$ )

- Minimum line width:  $2 \lambda$

- Main disadvantages:

- Limited linear scaling

- Too conservative

- Micron Based Design Rules

- Express designs in absolute dimensions

- Pro: Allow taking full advantage of technology

- Con: Scaling and Porting becomes more complicated

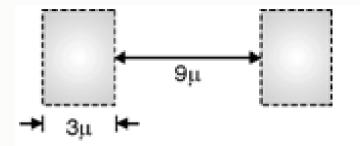

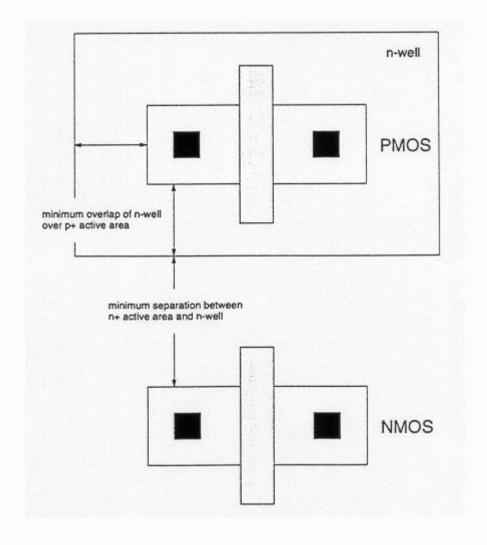

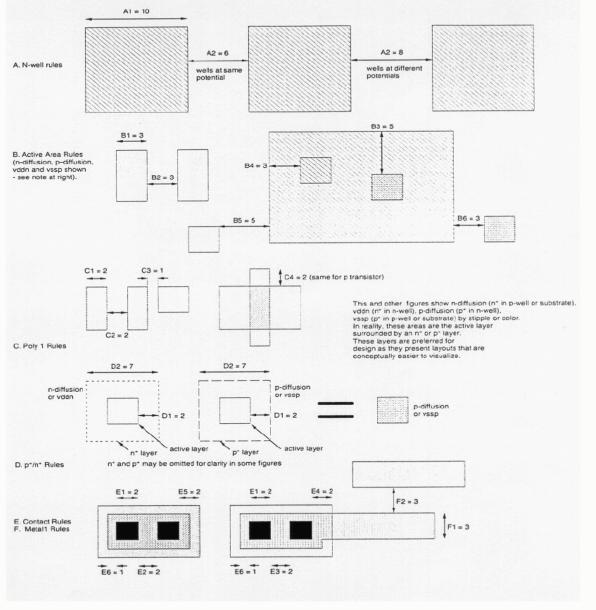

- (1) Rules for N-well as shown in Figure below.

- Width 3µ

- Space 9µ

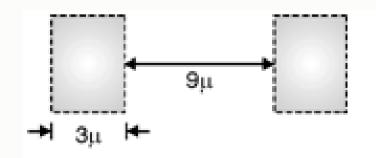

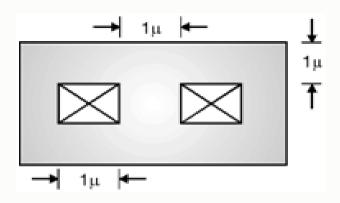

- 2) Rules for active area as shown in Figure below

- -1. Minimum size =  $3\mu$

- -2. Minimum spacing =  $3\mu$

- -2. N+ active to N-well =  $7\mu$

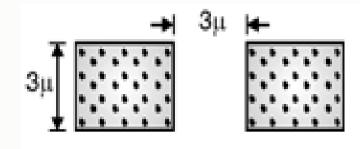

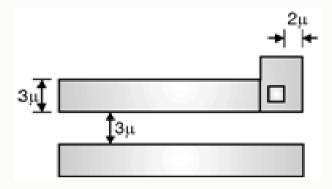

- (3) Rules for poly 1 as shown in Figure below.

- 1. Width =  $2\mu$

- 2. Spacing =  $3\mu$

- 3. Gate overlap of active =  $2\mu$

- 4. Field poly 1 to active =  $1\mu$

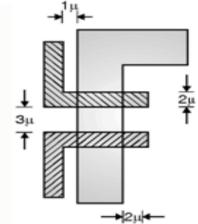

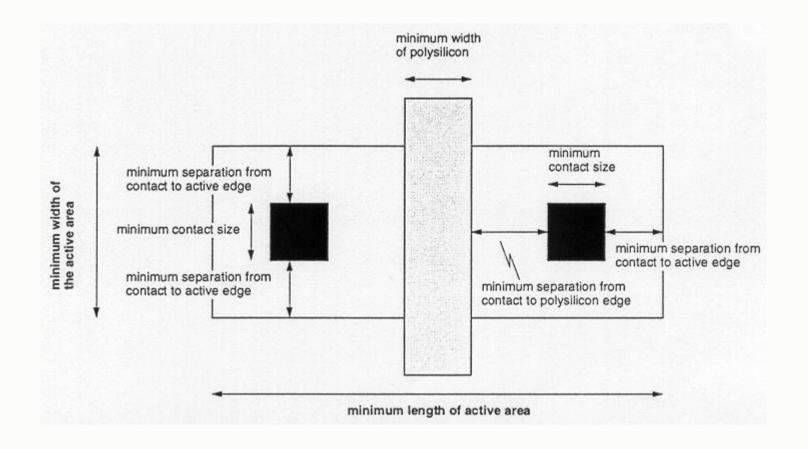

- 4) Rules for contact to Poly as shown in Figure below

- -1. Exact contact size =  $2\mu \times 2\mu$

- -2. Minimum Poly overlap =  $1\mu$

- -3. Minimum contact spacing =  $2\mu$

- (5) Rules for contact to Active as shown in Figure below.

- 1. Exact contact size =  $2\mu \times 2\mu$

- 2. Minimum active overlap =  $1\mu$

- 3. Minimum contact spacing= 2µ

- 4. Minimum spacing to gate=  $2\mu$

- 6) Rules for Metal 1 as shown in Figure below

- -1. Width =  $3\mu$

- -2. Spacing =  $3\mu$

- -3. Overlap of contact =  $1\mu$

- (7) Rules for Metal 2 as shown in Figure below.

- 1. Width =  $3\mu$

- 2. Spacing =  $3\mu$

- 3. Overlap of contact =  $1\mu$

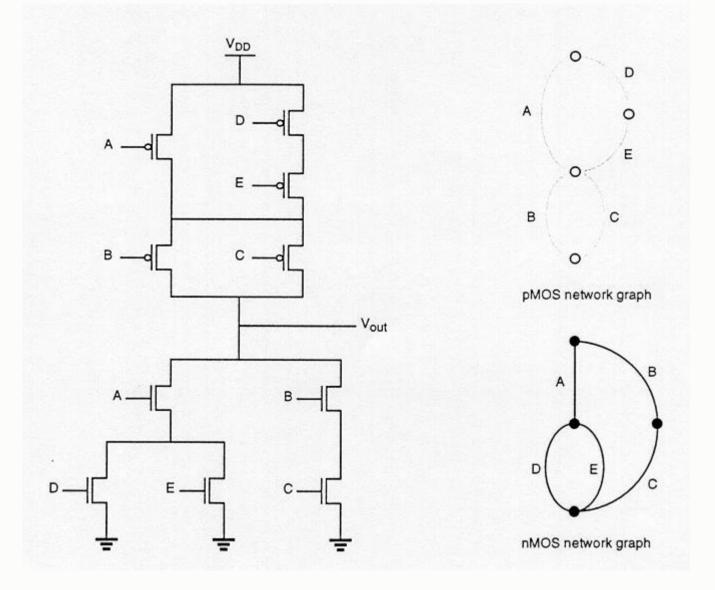

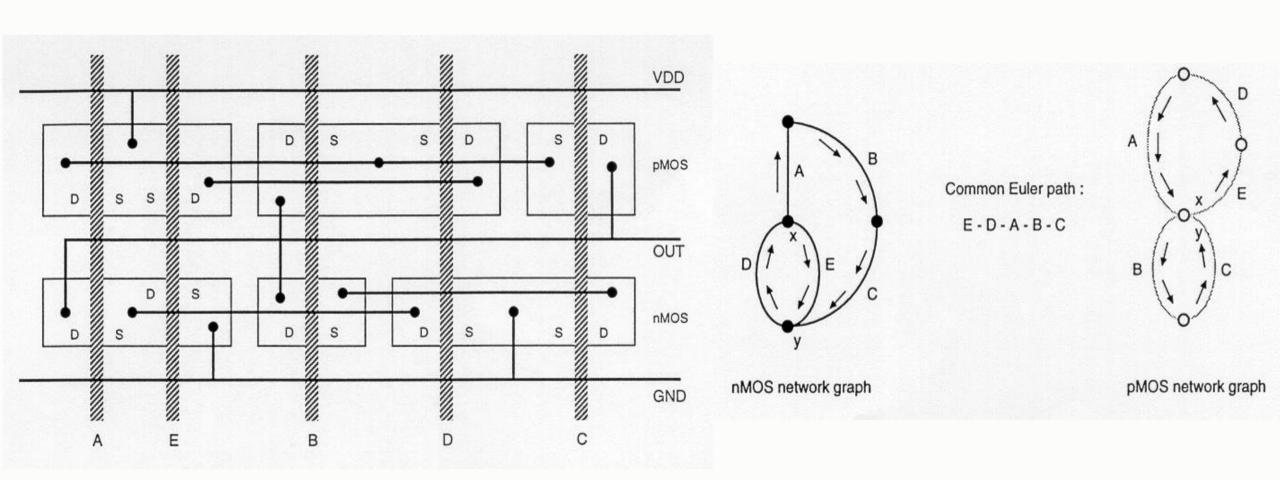

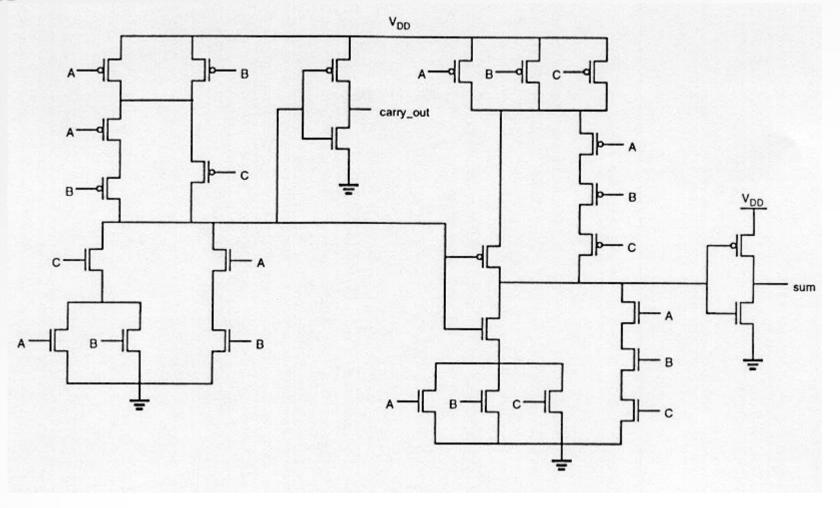

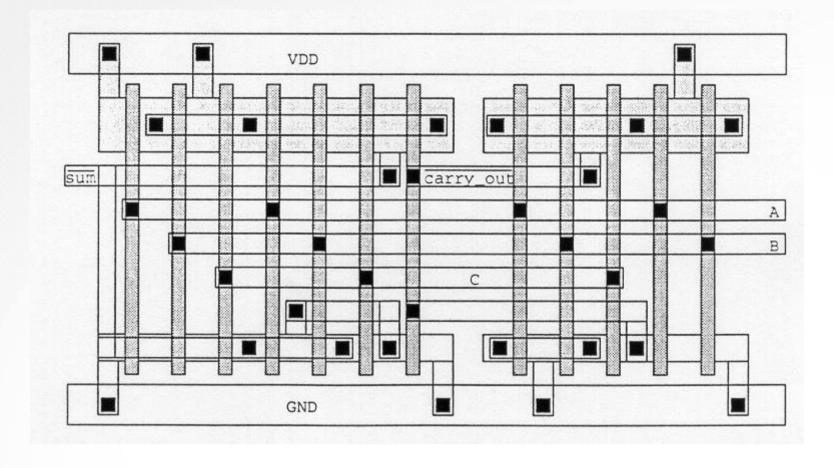

#### √ Full Adder

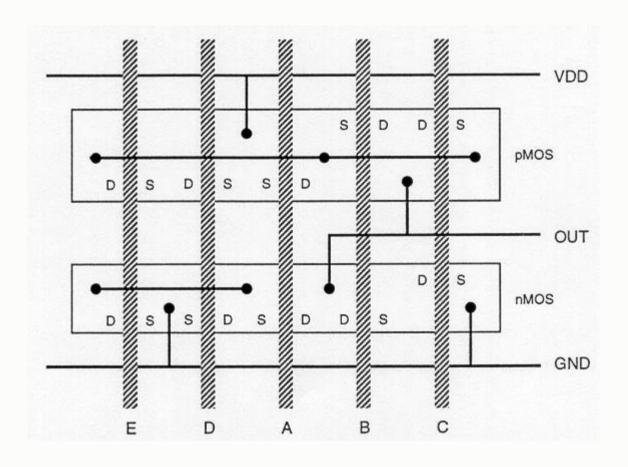

#### √ Full Adder Layout

# THANK YOU